Privacy Policy Update

Click here to learn about the new Privacy Policy updates from Practical Components.Package on Package (POP, PSVFBGA) Dummy Component-Amkor

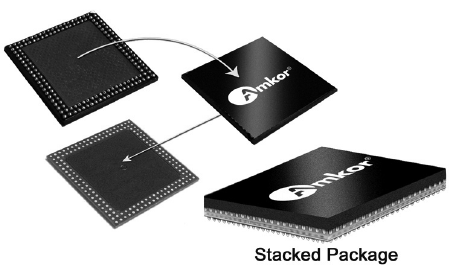

PoP

Package on Package (POP, PSVFBGA) Dummy Component-Amkor - Discontinued

Discontinued. Amkor is offering daisy chain samples of their award winning bottom Package Stackable Very Thin Fine Pitch BGA (PSvfBGA) and their top PoP optimized for Package on Package (PoP) requirements. PoP has become the solution of choice for an increasing number of mobile consumer applications for 3D integration of logic and memory devices. Amkor’s PSvfBGA is a high density fine pitch BGA package supporting logic or ASIC devices including base band, application and image processors. PoP stacking allows the OEM greater device, supplier and time to market flexibility by sourcing the bottom and top devices from their preferred logic and memory suppliers and then stacking the devices in the PWB surface mount assembly flow. A wide range of leading wireless and mobile integrated device manufacturers are relying on Amkor’s technical and industry leadership in PoP. Discontinued

|

PoP Package on Package—Mating Top and Bottom Daisy Chain Samples |

||||||

|

Part Description |

I/O Count |

Pitch |

Body Size |

Ball |

Ball |

Quantity |

|

12mm Body Size |

||||||

|

A-PoP128-.65mm-12mm-DC |

128 (top package) |

.65mm |

12mm |

18x18 |

Perimeter |

152 |

|

A-MPoP128-.65mm-12mm-DC |

128 (middle package) |

.65mm |

12mm |

18x18 |

Perimeter |

152 |

|

A-PSvfBGA305-.5mm12mm-DC |

305 (bottom package) |

.65mm (top) - .5mm (bottom) |

12mm |

23x23 |

Perimeter |

152 |

|

14mm Body Size |

||||||

|

A-PoP152-.65mm-14mm-DC |

152 (top package) |

.65mm |

14mm |

21x21 |

Perimeter |

119 |

|

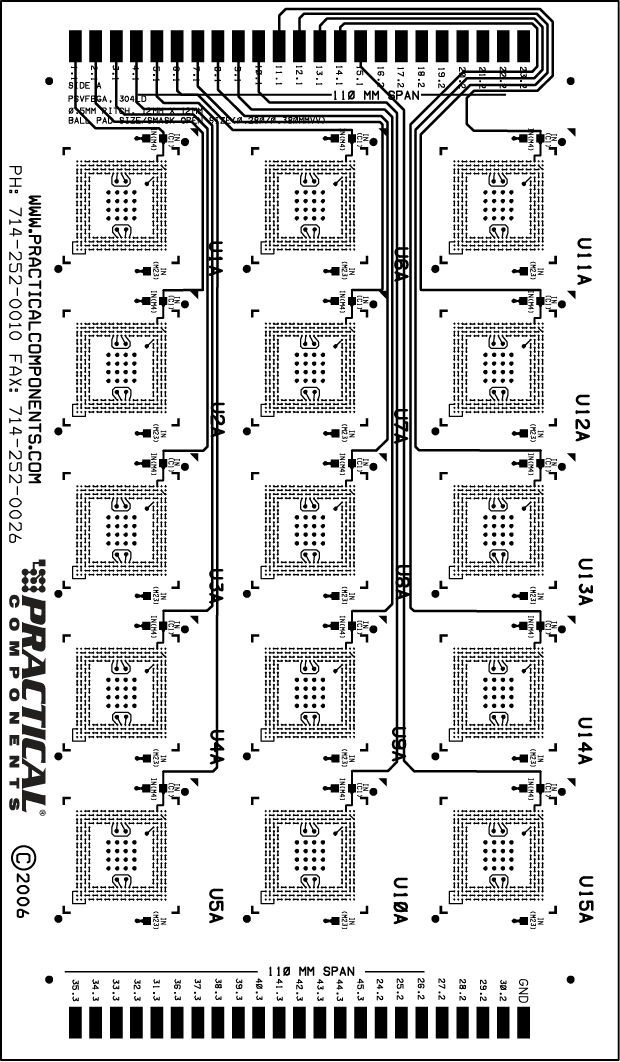

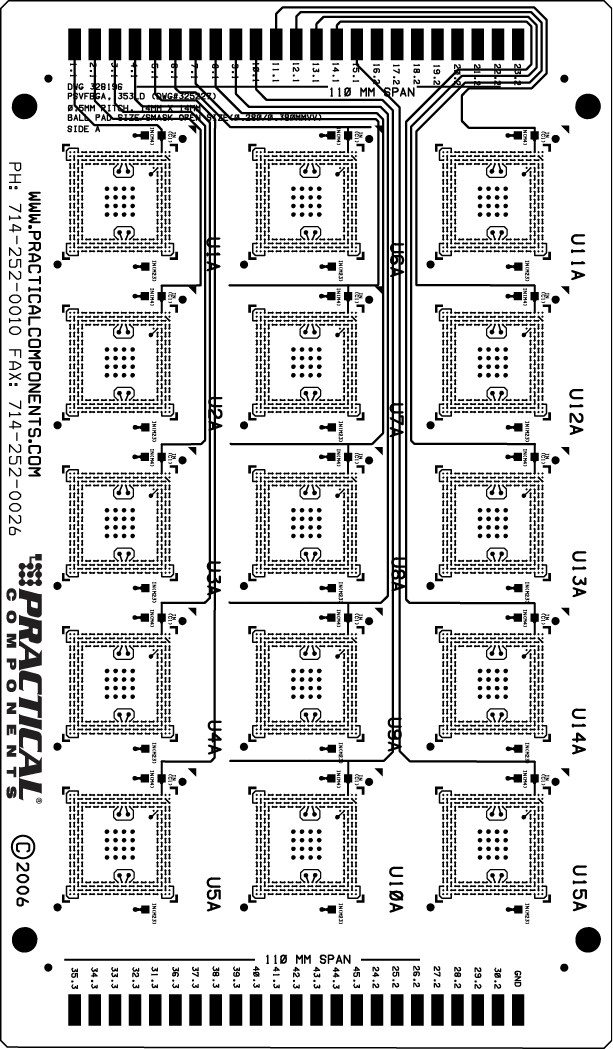

A-PSvfBGA353-.5mm-14mm-DC |

353 (bottom package) |

.65mm (top) - .5mm (bottom) |

14mm |

26x26 |

Perimeter |

119 |

|

15mm Body Size |

||||||

|

A-PoP160-.65mm-15mm-DC |

160 (top package) |

.65mm |

15mm |

22x22 |

Perimeter |

112 |

|

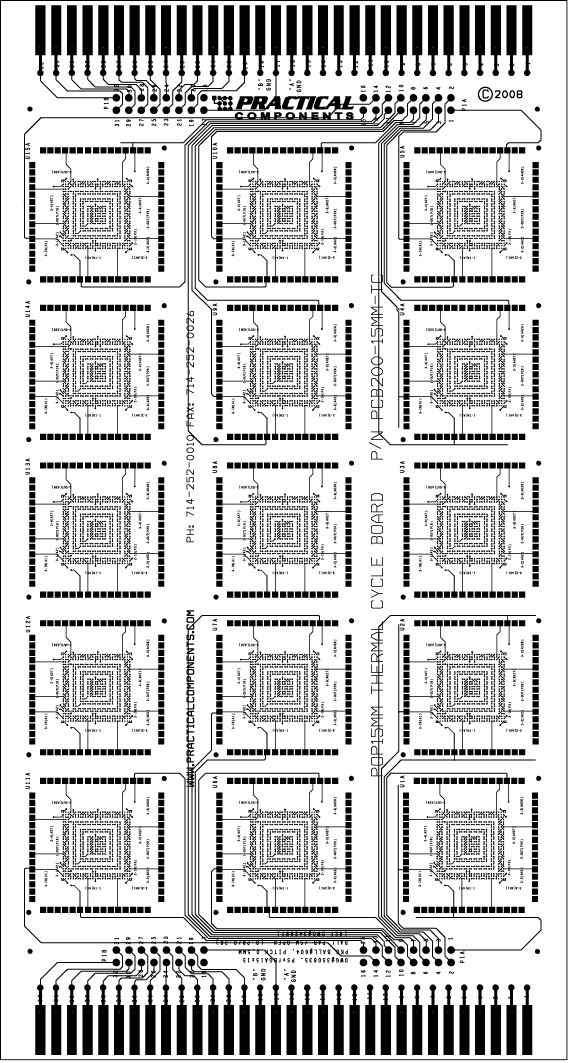

A-PSvfBGA604-.5-15mm-DC |

604 (bottom package) |

.65mm (top) - .5mm (bottom) |

15mm |

28x28 |

Perimeter |

112 |

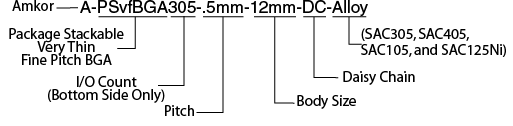

Part Description System

Notes

*Fine pitch 0.5mm bottom package footprints

*Stacked package heights of 1.2mm to 1.6mm available in a variety of configurations (see Stack Up table on following pages)

*Wafer thinning / handling < 100 µm

*Consistent product performance and reliability

*Package configurations compliant with JEDEC standards

*Moisture Resistance Testing is JEDEC Level 3 @ 260 °C

*Temp Cycle –55/+125 °C, 1000 cycles

*HAST 130 °C, 85% RH, 96 hours

*Temp/Humidity 85 °C/85%RH/1000 hours

*High Temp Storage 150 °C, 1000 hours

*Board level Thermal Cycle –40/+125 °C, 1000 cycles

*Parts packaged in JEDEC matrix trays

*PoPs are only available Pb-free (not Tin-Lead). Available alloys are: SAC305, SAC405, SAC105 and SAC125Ni*.

**SAC125Ni (98.25%Sn/1.2%Ag/0.5%Cu/.05%Ni) is only available for bottom packages.

*It is recommended that parts be pre-baked at 125 °C for 48 hrs before using parts regarding moisture concern.

*PoPs are not available without solder balls.

|

Ball Diameter |

|

|

I/O Count |

Ball Diameter |

|

128 |

0.45mm |

|

152 |

0.45mm |

|

305 |

0.30mm |

|

353 |

0.30mm |

Request Catalog

Request or download our catalog and sign-up for our newsletter.

Continue