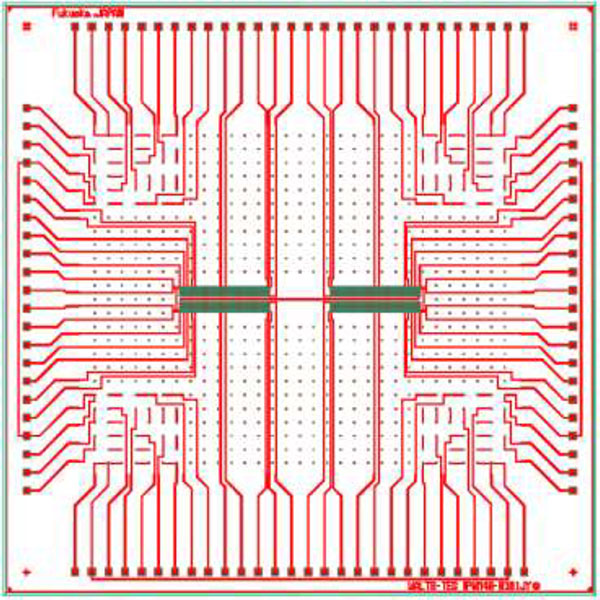

Practical Components-TEG IPWM40-0101JY

Chip Structure

- Base Layer : P-TEOS

- Metal layer : TiN / Al-0.5%Cu

- Passivation Layer : HDP / P-SiN

*TEOS : Tetraethoxysilane

| Specifications | |

| Wafer Size | 8 inch |

| Wafer Thickness | 725±25μm |

| Chip Size | 13.00mm x 13.00mm |

| Function |

Daisy Chain |

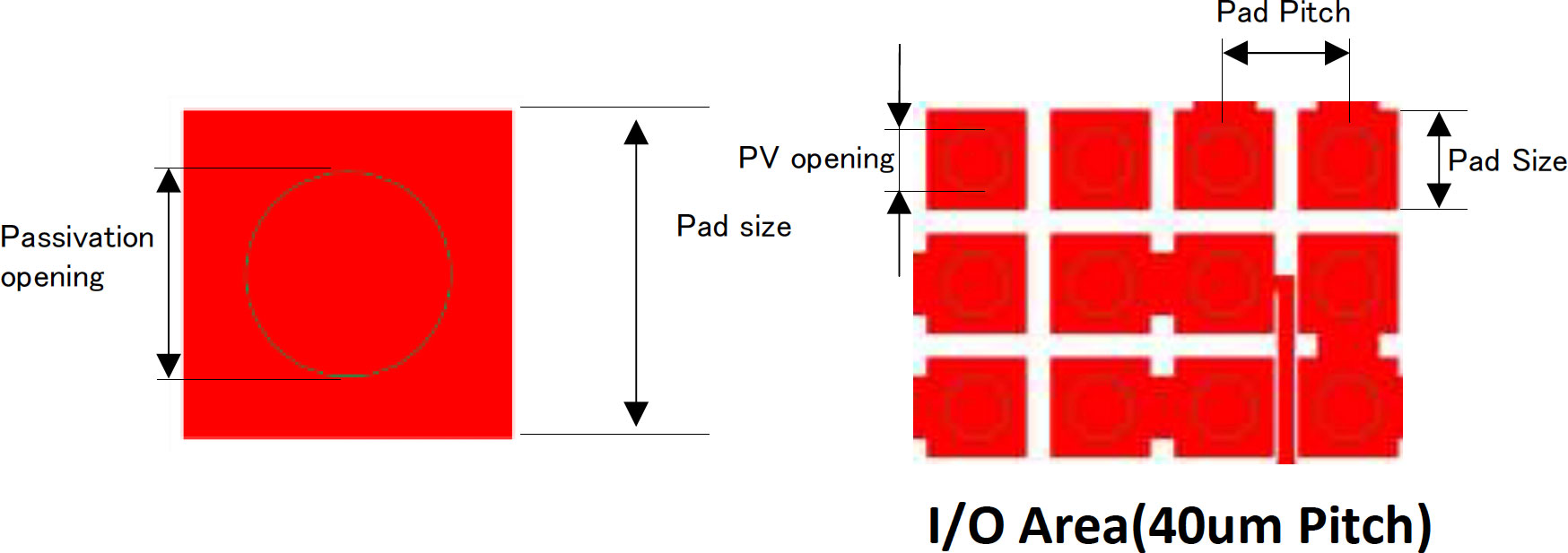

| Pad Size | 32μm |

| Passivation Operation | φ20um |

| Number of Pad |

1. 1200 pad |

| Electrode | Electroless Ni/Au plating |

| Bump Size | 25μm |

| Bump Pitch |

1. 40μm |

| Bump Height |

φ2.5um |

| Number of Chip |

148 chips/wafer |