Chip Structure

Practical Components MB80-STG0101JY advanced test wafer, 7.3mm chip size, 80μm staggered.

- Base Layer : P-TEOS*

- Metal Layer : TIN / AI-0.5%Cu

- Passivation Layer : HDP* / P-SIN (option) Polymide

*TEOS : Tetraethoxysilane

*HDP : High Density Plasma

| Specifications | TYPE-A | TYPE-B |

| Wafer Size | 8 inch | 8 inch |

| Wafer Thickness | 725±25μm | 725±25μm |

| Chip Size | 7.3mm ♦ | 7.3mm ♦ |

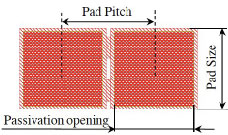

| Pad pitch | 80μm staggered | 80μm staggered |

| Function | Daisy Chain | Daisy Chain |

| Pad config | Peripheral | Peripheral |

| Electrode | Wire Bonding | Cu pillar |

| Pad Size | 76μm ♦ | 76μm ♦ |

| Bump Size | - | 38μm ♦ |

| Passivation opening | 70μm ♦ | 70μm ♦ |

| Scribe width | 120μm | 120μm |

| Number of Pad | 648 pads/chip 82pads×4(Outer line) 80pads×4(Inner line) |

648 pads/chip 82pads×4(Outer line) 80pads×4(Inner line) |

| Number of Chip | 478 chips/wafer | 478 chips/wafer |

| ♦ Bottom Side |