Practical Components MB50-0101JY advanced test wafer

Chip Structure

- Base Layer : P-TEOS*

- Metal Layer : TiN / AI-0.5%Cu

- Passivation Layer : HDP* / P-SiN (option) Polymide

*TEOS : Tetraethoxysilane

*HDP : High Density Plasma

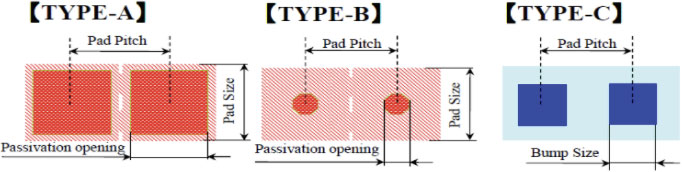

| Specifications | Type-A | Type-B | Type-C (Glass) |

| Wafer Size | φ 8 inch | φ 8 inch | φ 8 inch |

| Wafer Thickness | 725±25μm | 725±25μm | 700±70μm |

| Chip Size | 7.3mm | 7.3mm | 7.3mm |

| Pad Pitch | 50μm | 50μm | 50μm |

| Function | Daisy Chian | Daisy Chian | - |

| Bump Size | - | Au: 30µm Cu: 30µm Cu: φ25μm |

Cu: 30µm Cu: φ25μm |

| Bump Height | - | (Cu30μm+SnAg15µm) | (Cu30μm+SnAg15μm) |

| Number of Pad | 544 pads/chip | 544 pads/chip | - |

| Number of Chip | 478 chips/wafer | 478 chips/wafer | 478 chips/wafer |

| Polyimide (Option) | O | O | O |

| Evaluation KIT | WALTS-KIT MB50-0102JY_NCR [Standard] WALTS-KIT MB50-0104JY_CR [Standard] WALTS-KIT MB50-0105JY_CR [Standard] WALTS-KIT MB50-0102JY_NCR [MAP] WALTS-KIT MB50-0103JY_CR [MAP] WALTS-KIT MB50-0104JY_CR [MAP] |

||