Chip Structure

- Base Layer : P-TEOS*

- Metal Layer : TiN/ AI-1.0%Cu

- Passivation Layer : HDP* / P-SiN

*TEOS : Tetraethoxysilane

*HDP : High Density Plasma

| Specifications | |

| Wafer Size | 8 inch |

| Wafer Thickness | 725±25um |

| Chip Size | 7.3mm ♦ |

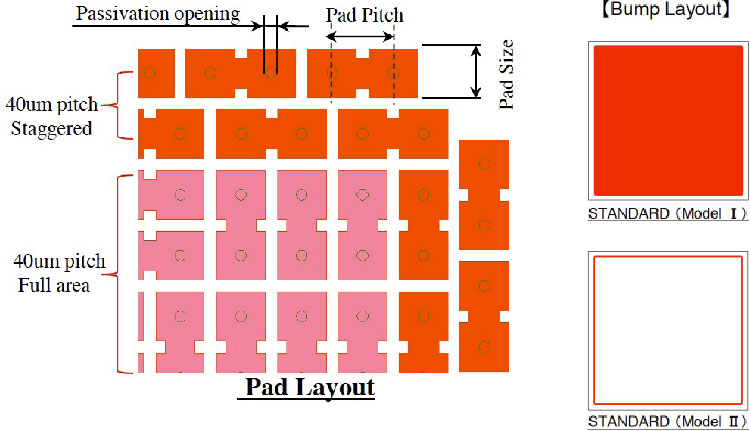

| Pad Pitch | 40μm pitch Full area + Staggered (Model I) 40μm pitch Staggered (Model II) |

| Function | Daisy Chain |

| Pad Config | Full Area (Model I) Peripheral (Model II) |

| Electrode | Cu pillar |

| Pad Size | 32μm ♦ |

| Passivation Opening | 7μm • |

| Scribe Width | 120μm |

| Number of Chip | 478 chips/wafer |

| • Top Side ♦ Bottom Side |

|

Bump Layout |

Bump Size |

Number of Bumps |

|

Model I |

φ22um |

29576 |

|

Model II |

φ22um |

1352 |