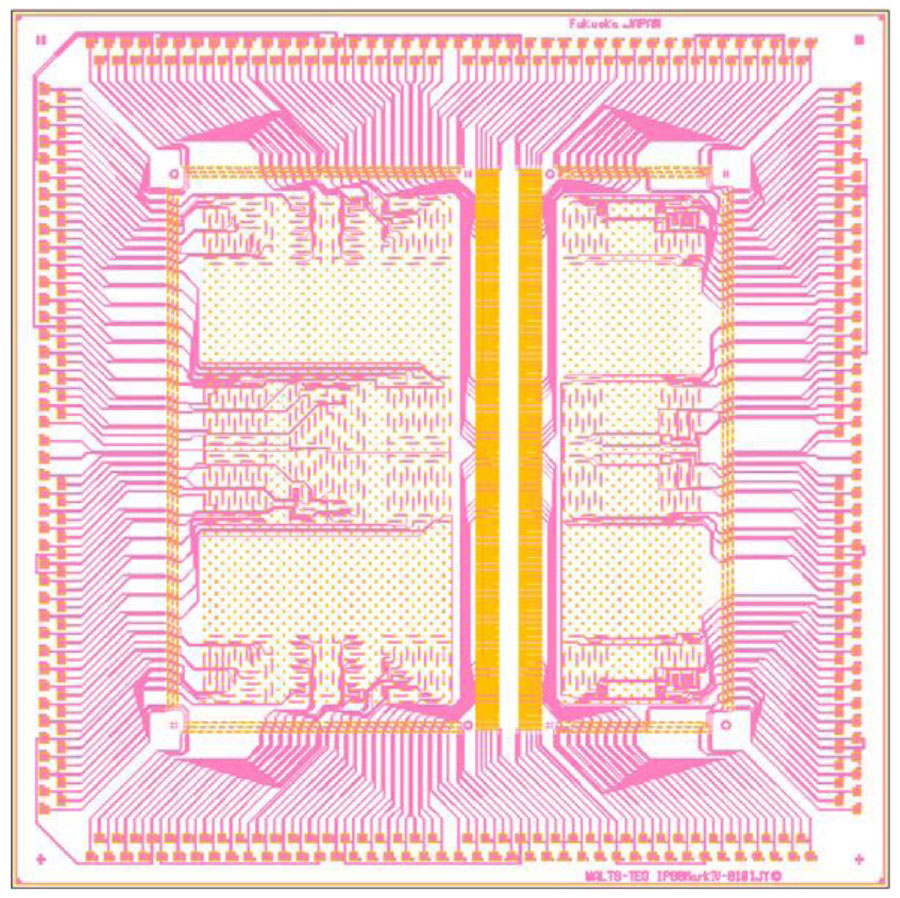

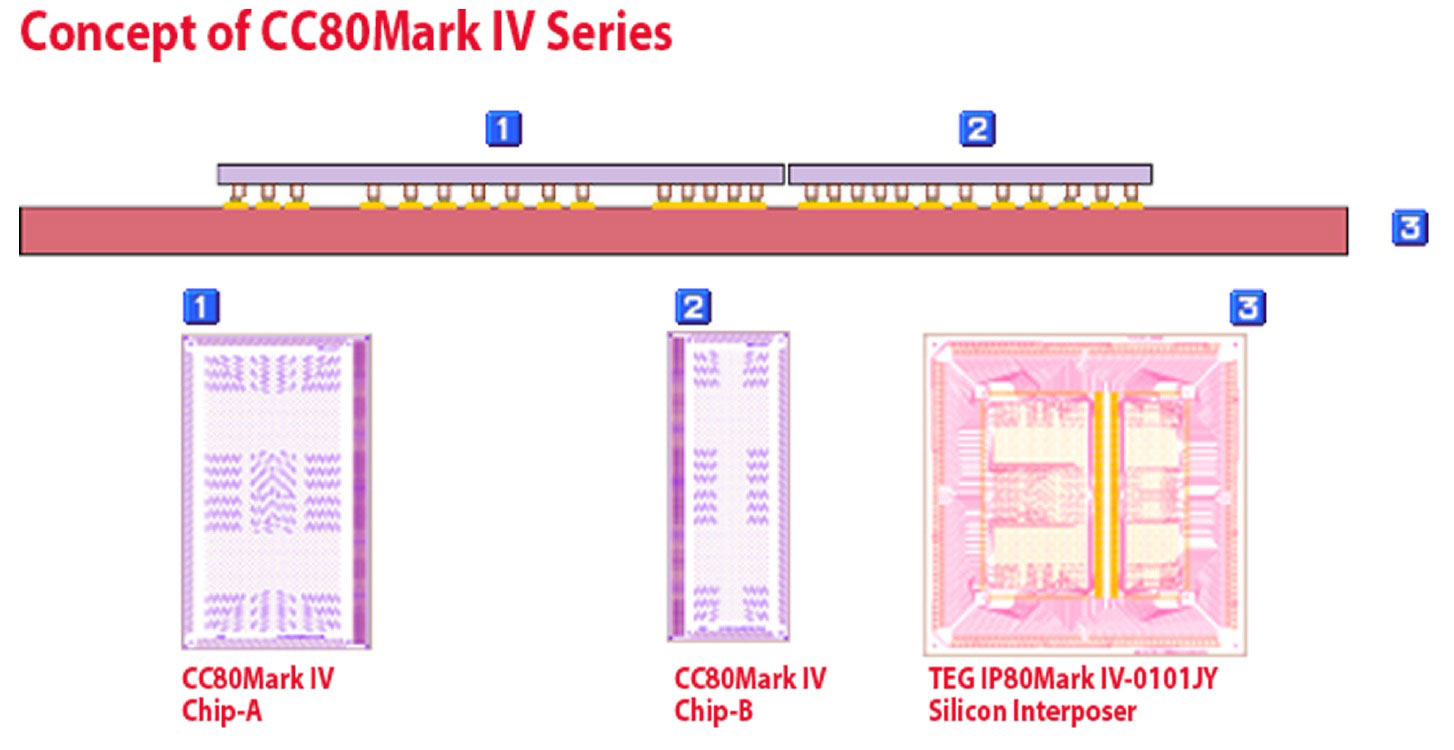

Practical Components IP80 MarkIV-0101JY advanced test wafer

Silicon Interposer [for CC80MarkIV-0101JY (A/B)]

Chip Structure

- Base Layer : P-TEOS

- Metal Layer : TiN / AI-0.5%Cu

- Passivation Layer : HDP / P-SiN

*TEOS : Tetraethoxysilane

*HDP : High Density Plasma

| Specifications | |

| Wafer Size | 8 inch |

| Wafer Thickness | 725±25μm |

| Chip Size | 15.0mm x 15.0mm |

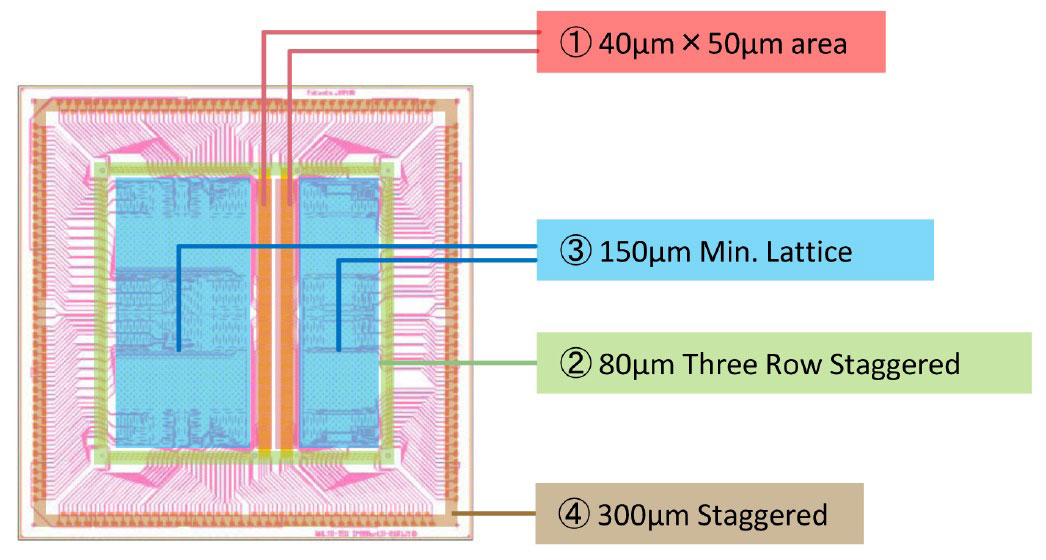

| Pad Pitch |

1. 40μm [10Row] x 50μm[192Row] x 2(Peripheral) |

| Function | Daisy Chian |

| Electrode | Electroless Ni/Au plating |

| Pad Size | 1. 32μm 2. 32μm 3. 32μm 4. 150μm |

| Passivation Opening |

1. 26μm |

| Bump Size | 1. 27μm 2. 27μm 3. 27μm 4. 141μm |

| Number of Bump/Pad | 1. 3840 bumps / 3840 pads 2. 1172 bumps / 1172 pads 3. 2721 bumps / 2721 pads 4. 328 bumps / 328 pads |

| Scribe Width | 120μm |

| Number of Chip | 97 chips/wafer |